对原Design执行DRC(Design Rule Checking),即设计规则检查。随着的复杂度升高,执行DRC可以显著提高Design的可测性,同时也检查Design的合理性。

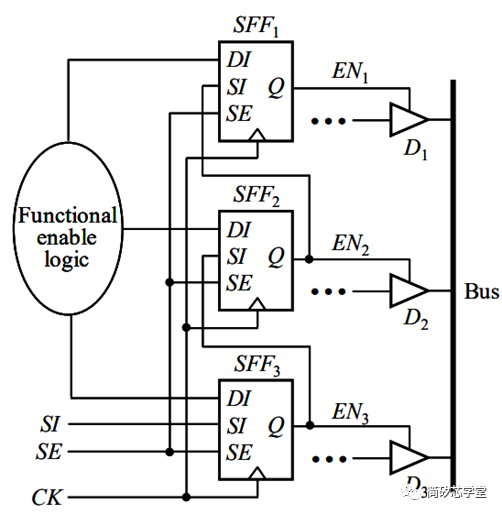

在Function模式下,由三态门严格控制,在同一总线上,同一时刻只允许一个设备向总线所示,三个寄存器的输入是DI,由Functional Enable Logic控制,在同一时刻Driver D1、D2、D3只有一个被使能,可以向总线输出数据。

但在测试模式下,ScanShift期间三个寄存器SSF1、SSF2、SSF3连成一条Scan Chain,输入由DI切换为SI,它们的值会根据测试pattern不停地变,无法保证3个Drivers在同一时刻只有一个驱动总线,这样就可能会引起总线竞争的问题。

为了避免这个问题,我们加入如图2所示的电路,当SE为1时,即Scan Shift期间,只有EN1为1,此时D1生效,D2和D3不生效。另外给总线加入Bus Keeper,使总线个Drivers均为高阻抗时保持总线上值不变。

但这样的设计依旧存在一个问题:在Scan Capture期间如何避免总线竞争问题?实际上这里的解决办法有好几种,笔者仅提供其中一种思路:在Capture期间SE的值为0,但TE(Test Enable ,图中未画出)依旧为1,我们可以利用TE信号来设计逻辑使得在SE为0时依然最多只有一个Driver被使能。

芯片上存在一些双向IOPin,如图3所示,由寄存器的输出Q来控制IO方向,当Q=1时是Output Pin,当Q=0时是Input Pin。但在Scan Shift期间,该寄存器的值会由于测试pattern而不停地变,从而导致I/O方向不断发生改变。

我们给原电路加入如图4所示的逻辑,当处于Scan Shift期间,SE的值为1,无论寄存器的值是0还是1,与门的输出均为0,这样就保证了在Scan Shift期间该IO PIN一直是Input Pin。当然也可以换成或门的逻辑,使该IO Pin在Shift期间一直是Output Pin。

如图5所示,这是一个非常简单的时钟门控电路,当enable为1时,gated clock与clock保持一致,当enable为0时,gated clock保持为1,即clock断开状态。但这样的设计无法很好地解决hazard,具体如图6波形图所示。

Designer为了解决这一问题,会采取如图7所示的设计:插入一个负沿触发的触发器,在时钟下降沿对enable信号进行采样,当enable为1时,将时钟打开,当enable为0时,将时钟关闭。这样就大大降低了hazard风险,波形图见图8。

然而这样做在测试中会引发另一个问题,那就是在Scan Shift期间该触发器的值会不断发生变化,我们也就无法控制时钟开关了。

假设原始的Design电路如图9所示,我们加入图10所示的逻辑 ,当SE为1时,Clock始终保持打开的状态,这样就保证了Scan Shift期间Clock门控电路始终打开。

本文所示案例在Function方面均属合理的设计,但并不利于测试,这也是引入DRC的重要意义。目前市面上不同的EDA工具对于Design Rule有着不同的规则体系,但本质是一样的,都是为了在插入DFT以及产ATPG Pattern之前消除潜在的风险并改善设计。

ca88手机登录地址